转自: http://blog.csdn.net/lightseed/article/details/4227299

LightSeed

2009-5-13

1、文章結構安排

上一篇有專門對PCI device的configuration space提法。那麼在這一節中我先做一個大體介紹,然後再對於一些特殊的比較有用的register做比較詳細的理解總結。

2、PCI配置空間介紹

2.1 configuration space的面貌

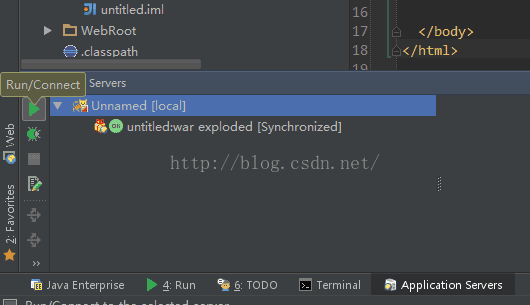

正如截圖1.1所示,這裡就是configuration space的面貌。

圖1.1 PCI配置空間的map

2.2 configuration space存在的原因

為了不產生歧義,我copy了spec里的原文,後面加上我自己的翻譯。“The intent of the PCI Configuration Space definition is to provide an appropriate set of configuration "hooks" which satisfies the needs of current and anticipated system configuration mechanisms, without specifying those mechanisms or otherwise placing constraints on their use. The criteria for these configuration "hooks" are:

• Sufficient support to allow future configuration mechanisms to provide:

• Full device relocation, including interrupt binding

• Installation, configuration, and booting without user intervention

• System address map construction by device independent software

• Minimize the silicon burden created by required functions

• Leverage commonality with a template approach to common functions, without precluding devices with unique requirements”

本PCI配置空间的定义是為了提供一系列合适的配置“鉤子”,它們可以满足现有的和预期的系统配置机制的需求,而不需指定這些机制,并且在它们的使用上也沒有作限定。这些配置“鉤子”的要点:

•为将来的配置机制提供充分支持:

•全部设备重定位,包括中断绑定

•安装、配置和開機无需用户干預

•系统地址映射是由与设备独立的软件來构造的

•在所需的功能下創建最小化的硅组件(這裡我也沒有懂啥意思>.<)

•平衡共用和特殊,对共同的功能使用模板方式实现,同时也不排除有独特需求的设备

(發覺真想直譯過來還挺麻煩的 ^.^)有點辭不達意,如果不是外行人我建議還是看英文原文比較好。起碼我是這麼想。

文字那麼一大堆,看的煩也煩死了。直接點,PCI設備要正常運作,那麼配置這些寄存器是必要條件。反之,沒有配置他們,PCI設備肯定是不能正常運作的啦。

3、幾個重點關注的register

3.1 Device ID and Vendor ID(offset 00H~03H)

之前有說明他們標誌了這個PCI設備的設備號,廠商代碼。具體要去查的話可以去查相應的組織。

3.2 Class Code(offset 09H~0BH)

這個寄存器是爲了標誌PCI設備用途的。分為這三個byte分別有各自的意義,詳細可以查一下spec。它是read only的。

3.3 Header Type(offset 0EH)

這個字節里的各個bit都有相應的用處,只是為了提高PCI scan才在這裡提一下,如果不用這個方法以現在的計算機速度,只用3個loops來PCI scan也不會有很大的延時的。

3.4 Base Address Register(BAR)

3.4.1寄存器作用

這些寄存器是重中之重。這次我懶得翻譯了,引用一下原文spec 2.3 page 205“One of the most important functions for enabling superior configurability and ease of use is the ability to relocate PCI devices in the address spaces. At system power-up, device independent software must be able to determine what devices are present, build a consistent address map, and determine if a device has an expansion ROM.”我想過了四級的人應該都能看的懂的。

3.4.2怎麼讀取BAR標誌的空間大小

那麼在build的過程中,BIOS怎麼才能知道pci設備需要多大的空間呢?在做PCI設備的時候,人們很聰明。當往BAR中寫0xFFFFFFFFH的后,再讀取BAR數值就會得到一個double word的數值。若返回是全“F”說明該BAR是不需要空間的,若返回非全F那麼從低位開始數,遇到第一個非“0”的bit時為止,從bit0~這位bitn(n<31)代表的大小就是PCI設備需要的空間大小了。

舉個例子:

當讀回來的數值是0xFFFFFC00H時,0xFFFFFC00H=1111 1111 1111 1111 1100 0000 0000B相信應該容易算出來了。

3.4.3BAR標誌的空間是memory還是IO?

細心的人會發覺在讀回來的數值中最低bit位有的是“0”,有的是“1”。他們究竟有什麽區別?簡而言之,“0”表示需要的是memory空間,“1”表示的是IO空間。詳細可以去看spec,他們都各自有各自的最小單位。

3.5 Interrupt Pin(offset 3CH)

引用一下Spec原文,因為我覺得他們說的比我說的清楚多了“The Interrupt Pin register tells which interrupt pin the device (or device function) uses. A value of 1 corresponds to INTA#. A value of 2 corresponds to INTB#. A value of 3 corresponds to INTC#. A value of 4 corresponds to INTD#. Devices (or device functions) that do not use an interrupt pin must put a 0 in this register. The values 05h through FFh are reserved. This register is read-only. Refer to Section 2.2.6. for further description of the usage of the INTx# pins.”PCI設備要處理數據,它的數據也肯定最終是要讓CPU來處理的,與CPU的通信的話PCI設備是通過中斷來實現的。而Interrupt Pin只是標誌了HW上用了INTx中的哪一個。這個與PCI IRQ routing table有關係了。後續篇章里我會繼續談到。

至此,configuration space中我覺得重要點的寄存器就算講的差不多了。以上均是我在學習的過程中都遇到過問題的,再次做一次小結。不對之處在所難免,望各位指正。這篇講概念性的東西比較多,但是卻都是必備的東東。

-

10楼

匿名用户 2010-03-31 22:57发表

[回复]

-

-

发一个稍微有点偏题的意见,最好能再讲下PCI EXPRESS.

我觉得PCI已经快被淘汰了。

-

9楼

wcc1982 2010-01-15 17:54发表

[回复]

-

-

请教lightseed:

我们可以向BAR里面写0xFFFFFFFFH,通过返回值知道PCI device需要多大的空间,那我们如何知道这个空间从哪开始?也就是它的开始地址是什么?-

Re:

匿名用户 2010-03-24 18:07发表

[回复]

-

- 回复 wcc1982:这个起始地址要你自己填进去啦

-

-

8楼

lightseed 2009-10-07 20:44发表

[回复]

-

-

to goldencrest ;

1,这个配置空间其实是一个(逻辑上的)地址空间,我打个比喻吧(因为我也没有追根去看是不是这样),这个空间类似于EEPROM一样的东西,只是这个EEPROM比较特殊点罢了(有些可写,有些只可读等特性)。

2,这个问题你再看看,“3.4.2怎麼讀取BAR標誌的空間大小”这一小节,说的比较清楚,或者我建议你看看sepc第六章的相关部分,当然spec说的比较隐晦,但是意思却很明了。

-

7楼

goldencrest 2009-10-07 14:28发表

[回复]

-

-

to lightseed: 谢谢你这么及时的回复。 还是有点疑问。

1)如果configuration space是厂商提供好的,那么这些东西放在pci 设备的什么地方。

2)像base address这种东西,应该是系统BIOS给分配的,厂商不应该事先知道,这类信息怎么理解?

-

6楼

lightseed 2009-10-07 14:17发表

[回复]

-

-

to goldencrest ;

系统软件可能需要扫描PCI总线,以便确定总线上实际连接的设备。为此,配置软件读取每个PCI槽位上的设备供应商识别代码。如果所读取的位置上不存在设备,则主桥必须准确无误地报道出来。OFFFH是一个非法的设备供应商识别码。如果设备不存在,则主桥可以通过返回一个二进制全为“l”的值来作为设备配置空间寄存器的读出值。

-

5楼

lightseed 2009-10-07 14:17发表

[回复]

-

-

to goldencrest ;

PCI总线配置空间是容量为256字节并具有特定记录结构的一个地址空间,该空间分为头标区和设备相关区两部分。在每个区中,设备只设置必须的和与之相关的寄存器。一个设备的配置空间不仅在系统自举时可以访问,在其他时间也可以访问。

头标区的长度为64字节,偏移地址从00H到3FH,该区中的各个域用来识别各自不同的设备,并使设备能以一般的方法控制。每个设备都必须按照该区的格式和规定进行设置。而配置空间的其余192字节可以因设备而异。

-

4楼

lightseed 2009-10-07 14:13发表

[回复]

-

-

to goldencrest ;

这里说的pci configuration space就是指我们平时用CF8H,CFCH直接操作的那个space。它当然是由PCI的设备厂商就提供好的了。我们BIOS在做相应的initial的时候其实只是把space里面的值设置成更优化的value而已。本身它是存在的。至于BIOS在做的过称中可能为了方便等等会把一些重要的信息以结构体的形式做成一张表放在memory的某个地方,这样在配置的过称中就不用去反复从io端口去读取了。提高了效率也容易操作。

-

3楼

goldencrest 2009-10-07 08:25发表

[回复]

-

- 请教ligntseed一个问题,这里讲的configuration space到底是谁在maintain? 假设有一个video card, 那么这些configuration space里面的东西都是video card厂商写在卡上的某个位置? 还是SYSTEM BIOS在initialization 过程中,综合从option rom中得到一些信息,maintain在memory里的一张表?

-

2楼

lightseed 2009-07-22 09:09发表

[回复]

-

-

恩,qqhao一语中的!

是的,我们的header type其实挺重要的,我也只是在这里(pci scan)的时候才提了一下。我个人觉得pci configuration space都挺重要的,因为里面就是pci东西的一个缩影,不知道您这么认为么?

-

1楼

qqhao 2009-07-21 15:51发表

[回复]

-

- 印象中 header type 还是蛮重要的哟,除了区分multi-function 以外,还用来区分出 p2p bridge,即所谓的10h以后的定义...